# Performance Improvement of QPSK Modem with AWGN Implemented in FPGA

Umesharaddy1, B.K.Sujatha2

**Abstract:** This paper presents the methods to design optimized QPSK MODEM with AWGN. The Proposed methods consume less time, power and give better throughput using Spartan-3 and Sparatn-6 FPGA boards. The whole module is divided into several sub modules and those modules are designed using the verilog HDL. Finally, these modules are invoked and integrated to design top level module. Here, two different approaches are used to design the QPSK modulator and they are compared with a conventional QPSK modulator which is designed using arithmetic multipliers and adders. In one of the proposed methods, the modulator is designed by using Vedic multiplier and carry look-ahead adder and demodulator is designed using an FIR LPF with AWGN. The FIR LPF coefficients are generated in MATLAB using a rectangular window and hamming window with AWGN. In the second method, QPSK modulator is designed using multiplexers. The QPSK module is implemented on Spartan-3 and Spartan-6(Atlys) FPGA board. The whole system has been simulated in Xilinx 14.7 and implemented on to the chips XC3S400-4pq208 and XC6SLX45 - CSG324. The results show that the proposed methods can greatly improve the speed and reduce the latency and improve the frequency of operation.

## Keywords: QPSK, FPGA, MODEM, HDL, AWGN, SDR, FIR.

#### I. INTRODUCTION

The advancements in wireless communication technology using various digital modulation techniques to transmit data with extreme low power have led us to use the concept of software defined radio (SDR). The process, where more and more hardware components are replaced with software, has resulted in coining the term SDR - because if the components can be replaced with software, then indeed the very functionality of these components can be redefined by using this software. By writing a new program module, a software radio is able to interoperate with different wireless protocols, incorporate new services, and upgrading to new standards.

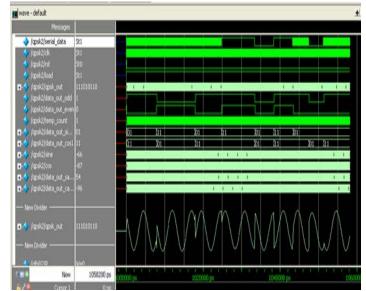

Present software-defined radios (SDR) employ front end circuits that contain multiple receivers and transmitters for each band of interest, which is inflexible, expensive and power inefficient [4]. A programmable front end circuit is implemented on a CMOS device and is configurable to transmit and receive signals in a wide band of frequencies, thereby providing an adaptable transmitter and receiver operable with current and future wireless networking technologies. In this paper, the FPGA implementation of QPSK modulator using two different methods, i.e., proposed method-1 and proposed method-2[1] and comparison with the conventional QPSK modulator method is done and also demodulator design for proposed method-1 is presented with AWGN [16]. Complete modulator and demodulator units are modeled using Verilog and functionality is verified using I-

Sim simulation tool [6] [11]. The code is synthesized fully onto Xilinx FPGAs.

Parts of this paper were presented at the IEEE 2015 IC-SSS Conference.

Umesharaddy, Asst. prof Dept. of Telecommunication Engineeringg Ramaiah Institute of Technology, Bangalore-560054, Karnataka India, e-mail: umesh.reddy@msrit.edu

B.K.Sujatha, Professor Dept. of Telecommunication Engineeringg Ramaiah Institute of Technology, Bangalore-560054, Karnataka, India, e-mail: bksujatha@msrit.edu

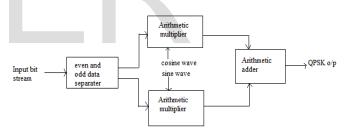

## II. CONVENTIONAL QPSK MODULATOR

In this method the input 16 bit stream is divided into even and odd components of 8-bits each. These even and odd components are multiplied with cosine and sine waves respectively using normal arithmetic multiplier and finally these In phase and Quadrature phase components are added using normal arithmetic adder as shown in Figure 1.

Figure 1. Proposed conventional QPSK modulator.

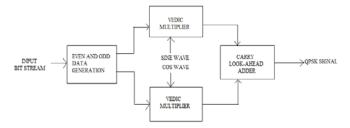

## III. PROPOSED METHOD-1 QPSK MODEM WITH AWGN

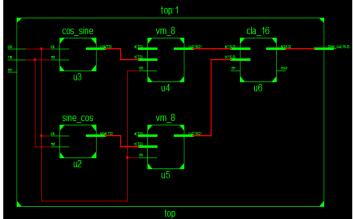

Proposed Method - 1 of QPSK modulator is designed by using Vedic multiplier (VM) and Carry Look Ahead adder (CLA) [2]. The input bit stream is divided into even and odd bits and multiplied by cosine and sine wave respectively using Vedic multiplier instead of normal arithmetic multiplier and later adding the in phase and quadrature phase component using carry look-ahead adder instead of normal arithmetic adder as shown in Figure 2[3].

Figure 2. Proposed Method-1 QPSK Modulator

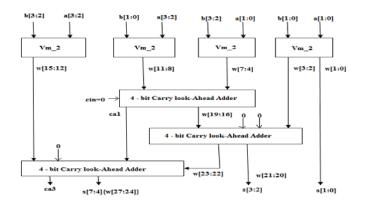

The 4x4 bit Vedic multiplier module is implemented using four 2x2 bit Vedic multiplier modules as discussed and also 4bit carry look ahead adder is implemented to reduce the ripples of carry so that performance can be improved shown in Figure 3.

Figure 3. 4 Bit Vedic Multiplier

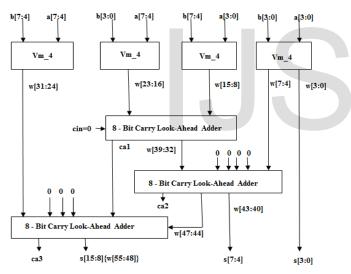

Similarly using 4-bit vedic multiplier 8-bit vedic multiplier can be designed and using 8-bit vedic multiplier 16-bit vedic multiplier can also be designed and so on as shown in the Figure 4 and Figure 5 below [8].

Figure 4. 8 Bit Vedic Multiplier

**Figure 5.** 16 Bit Vedic Multiplier **A. PROPOSED METHOD-1 QPSK DEMODULATOR WITH AWGN:**

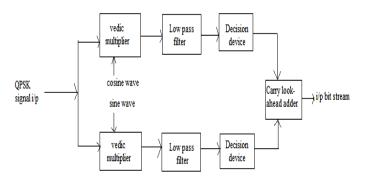

The previously designed Vedic multiplier and CLA blocks as described previously are used in designing the QPSK demodulator module along with FIR (Finite impulse response) Low pass filter designed using Hamming window with AWGN as shown in Figure 6.

Figure 6. QPSK Demodulator for Proposed method-1 with AWGN

#### **B. PROPOSED METHOD-2 OF QPSK MODULATION**

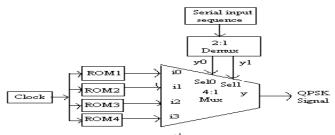

For the second QPSK modulator architecture, the above proposed QPSK modulator 1 architecture will be constructed just to collect four different combinational input data for different phases of QPSK. Once the data is collected, the first proposed OPSK modulator architecture will not be used for future method. In this method, data for each OPSK is collected and stored in four different ROM blocks. Each ROM will store data for one QPSK phase. Since all the four possible phases for a QPSK is stored in four different ROM's, the digital QPSK modulator is no longer required to produce a QPSK phase from I and Q phase as in first method QPSK modulator[18]. For the simulation purposes, a serial input sequence will be considered as input to the 1:2 demultiplexer. The 1:2 demultiplexer will separate the input sequence into odd and even bits. These odd and even bits will be the input for the 4:1 multiplexer which will select one ROM for different combination of odd and even bits as shown in Figure 7.

Figure 7. Block diagram for 2<sup>nd</sup> proposed QPSK modulator

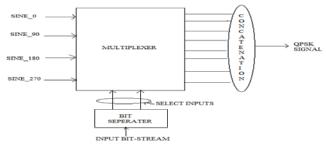

In this modulation technique the input sixteen bit data bit stream is divided into two bits at a time. These two bits 00,10,01,11 act as the select lines for the multiplexer which selects sine with 0 degree, sine with 90 degree, sine with 180 degree and sine with 270 degree phase shifts respectively. Then all these are concatenated to get the final QPSK wave.

Below Figure 8 shows implementation of QPSK modulator with elaboration using multiplexer concept[10].

Figure 8. Elaboration of Proposed method -2 of QPSK modulator

## **IV. SIMULATION RESULTS**

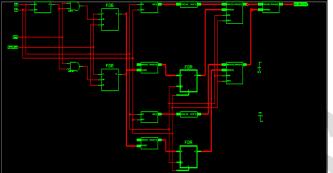

Figure 9 shows the RTL obtained by synthesizing Verilog HDL code for conventional QPSK modulator. Figure10 shows the simulator timing diagram, where odd and even data change from 00 to 01 and 11 to 10. Then the data obtained is multipled with carrier wave generator to produce I and Q phases and then added to both phases to generate QPSK signal. Here DDS is used and design 16 phases to generate sine and cosine wave.

Figure 9. Top level RTL for conventional QPSK modulator

Figure 10. Simulation result of conventional QPSK modulator

Figure 11 represents the output of carry look-ahead adder where, a and b are the inputs which are 8-bit wide and cin is the carry input which should be zero for addition operation. s, p and g are the sum, carry generate and carry propagate respectively each of 8- bit width, cout is the output carry of one bit.

|                       |          | 6,999,6                                                                      | 997 ps |

|-----------------------|----------|------------------------------------------------------------------------------|--------|

| Name                  | Value    | 5,999,992,ps (5,999,993,ps (5,999,994,ps (5,999,995,ps (5,999,996,ps (5,999, | 997 ps |

| 🕨 👫 a[7:0]            | 255      | 255                                                                          |        |

| 🕨 📲 b(7:0)            | 255      | 255                                                                          |        |

| ll <mark>a</mark> cin | 0        |                                                                              |        |

| ▶ 🕌 s[7:0]            | 254      | 254                                                                          |        |

| lla cout              | 1        |                                                                              |        |

| 🕨 👹 p[7:0]            | 0000000  | 0000000                                                                      |        |

| 🕨 👹 g[7:0]            | 11111111 |                                                                              |        |

| 🕨 🕌 c[7:0]            | 11111111 |                                                                              |        |

|                       |          |                                                                              |        |

|                       |          |                                                                              |        |

|                       |          |                                                                              |        |

|                       |          |                                                                              |        |

|                       |          |                                                                              |        |

Figure 11. Carry look-ahead adder results

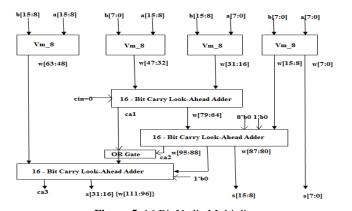

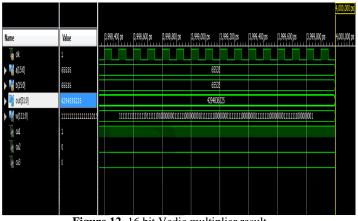

Here a and b represents the inputs to the Vedic multiplier each of 16 bits width and output of Vedic multiplier is out which is of 32 bits, and ca1,ca2,ca3 represents the intermediate carry outputs from the carry look ahead adders used in the design.

Figure 12. 16 bit Vedic multiplier result

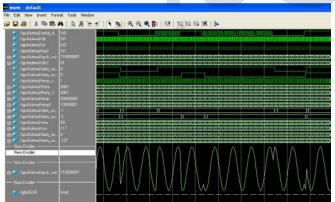

This represents sine and cosine waveforms generated in Modelsim 6.1 version

Figure 13. Sine and cosine wave generation in Modelsim

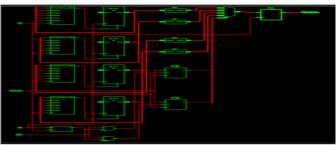

Figure 14. RTL schematic for proposed method-1 with AWGN.

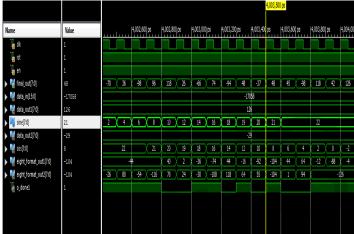

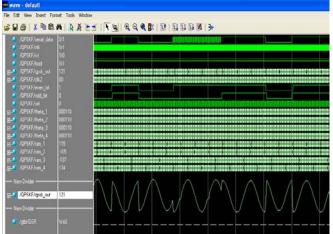

This represents the final QPSK output in digital format generated using ISim inbuilt simulator present in Xilinx 14.7 version. final\_out is the QPSK output and clk, rst, en and data\_in are the inputs.

Figure 15. QPSK modulation for proposed method-1 in ISim simulator with AWGN.

Figure 16. Simulation result of proposed QPSK Modulator 1 in Model simulator from mentor graphics EDA tool.

|                      |                   |     |       |          |       | <b>4</b> | al re <sup>l</sup> cu |       |          |       |          |       |          |        |          |

|----------------------|-------------------|-----|-------|----------|-------|----------|-----------------------|-------|----------|-------|----------|-------|----------|--------|----------|

| Name                 | Value             | İ., |       | 2,649,80 | 0.ps  |          | 2,650,000             | ps    | 2,650,20 | 0 ps  | 2,650,40 | 0 ps  | 2,650,60 | ) ps   | 2,650,80 |

| 🕨 🕌 qpout(15:0)      | 1011100010101111  | U   | 10101 | 10011    | 10111 |          | 01010                 | 10011 | 00000    | 10010 | 01000    | 01000 | 10000    | 11111  | 10110    |

| inal_out[15:0]       | 0110010010110100  | 1   | 10010 | 10000    | 01100 |          | 01111                 | 01100 | 10000    | 10100 | 10100    | 01011 | 01100    | 10100  | 00111.   |

| l <mark>ia</mark> ek | 0                 |     |       |          |       |          |                       |       |          |       |          |       |          |        |          |

| l <mark>e</mark> ist | 0                 |     |       |          |       |          |                       |       |          |       |          |       |          |        |          |

| la en                | 1                 |     |       |          |       |          |                       |       |          |       |          |       |          |        |          |

| 🕨 🙀 data_in(15:0)    | 10111101010111110 |     |       |          |       | ī        |                       |       |          |       |          | 10111 | 01010111 | 10     |          |

| ▶ 📲 data_out1[7:0]   | 01111110          |     |       |          |       |          |                       |       |          |       |          | 0     | 111110   |        |          |

| ▶ 🍇 sine[7:0]        | 01110101          | 0   | 00110 | 01011    | 01110 |          | 01111                 | 01110 | 01011    | 00110 | 00000    | 11001 | 10100    | 10001  | 10000.   |

| 🕨 🙀 data_out2(7:0)   | 11100011          |     |       |          |       |          |                       |       |          |       |          | 1     | 1100011  |        |          |

| 💐 cos[7:0]           | 00110001          | 0   | 01110 | 01011    | 00110 |          | 00000                 | 11001 | 10100    | 10001 | 10000    | 10001 | 10100    | 11001  | 00000.   |

| ▶ 🍇 data_out3(15:0)  | 1010101011100011  | 0   | 10100 | 10010    | 10101 | D        | 01001                 | 10010 | 11111    | 10001 | 00111    | 00111 | 01110    | 11111_ | 10110.   |

| ▶ 💐 data_out4(15:0)  | 1101000001010011  | 1   | 10000 | 01111    | 11010 |          | 10111                 | 01111 | 00100    | 01111 | 10000    | 11011 | 11111    | 00000  | 00101.   |

| 🕨 🍇 data_oud5(15:0)  | 0000100110011000  | ۵   | 00001 | 00001    | 00001 | D        | 00000                 | 00001 | 00001    | 00001 | 00000    | 00000 | 0000     | 00001  | 00001    |

| 🕨 🙀 data_outb(15:0)  | 0000110111001100  | U   | 00001 |          | 00001 |          | 00001                 | 0000  | 03033    | 00000 | 00001    | 00001 | 00001    |        | 0000.    |

| ▶ 🍕 sine_1(150)      | 000000001111110   |     |       |          |       | f        |                       |       |          |       |          | 00000 | 00111111 | 10     |          |

Figure 17. QPSK demodulation for proposed method-1 in ISim simulator with AWGN.

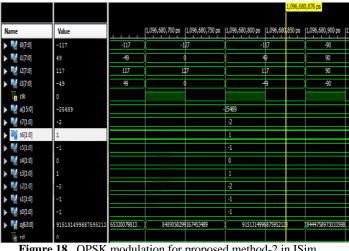

Figure 18. QPSK modulation for proposed method-2 in ISim simulator.

Figure 19 shows the RTL schematic diagram and Fig.20 shows the simulator timing diagram. Since the data for each QPSK phase is collected and stored in four different Read Only Memory (ROM) blocks. Once the four phases QPSK modulator data is collected from proposed QPSK modulator 1, conventional QPSK modulator is no longer required. A group of 2 bits is used to represent a phase in QPSK waveform. A total number of 50 data stored in each ROM to represent a phase in QPSK wave. Fig.8 shows the baseband data transition form 00, 01, 11 and 10.

Figure 19. RTL schematic for proposed method-2

209

This represents the QPSK output generated by proposed

method-2 using multiplexer concept.

Figure 20. Simulation result of proposed QPSK modulator 2

## FIR Low Pass Filter output designed using Hamming and Rectangular window in MATLAB.

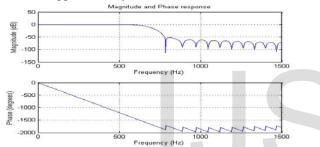

The below Figure 21 represents the magnitude and phase response of Low Pass Filter designed using hamming windowing technique. Here, the cutoff frequency of the filter is 800 Hz approximately[12].

Figure 21. FIR Low pass filter output using Hamming window

| 0.0010  | 0.0011  | -0.0008 | -0.0024 | 0.0002  | 0.0045  | 0.0021  | -0.0069 | -0.0072 |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0.0079  | 0.0156  | -0.0048 | -0.0271 | -0.0059 | -0.0399 | 0.0298  | -0.0519 | -0.0831 |

| 0.0603  | 0.3097  | 0.4357  | 0.3097  | 0.0603  | -0.0831 | -0.0519 | 0.0298  | -0.0399 |

| -0.0059 | -0.0271 | -0.0048 | 0.0156  | 0.0079  | -0.0072 | -0.0069 | 0.0021  | 0.0045  |

| 0.0002  | -0.0024 | -0.0008 | 0.0011  | 0.0010  |         |         |         |         |

Table 2: Filter Coefficients generated using rectangular window

| 0.008  | 0.0011  | -0.0002 | -0.0018 | -0.0015 | 0.0017 | 0.0042  | 0.0012  | -0.0058 | -0.0073 | 0.0023  | 0.013  |

|--------|---------|---------|---------|---------|--------|---------|---------|---------|---------|---------|--------|

| 0.0085 | -0.0122 | -0.0236 | -0.0032 | 0.0323  | 0.0345 | -0.0182 | -0.0740 | -0.0428 | 0.1074  | 0.2939  | 0.378  |

| 0.2939 | 0.1074  | -0.0428 | -0.0740 | -0.0182 | 0.0345 | 0.0323  | -0.0032 | -0.0032 | -0.0236 | -0.0122 | 0.0085 |

|        |         |         |         |         |        |         |         |         |         |         |        |

| 0.013  | 0.0023  | -0.0073 | -0.0058 | 0.0012  | 0.0042 | 0.0017  | -0.0015 | -0.0018 | -0.0002 | 0.0011  | 0.008  |

## A. HARDWARE IMPLEMENTATION

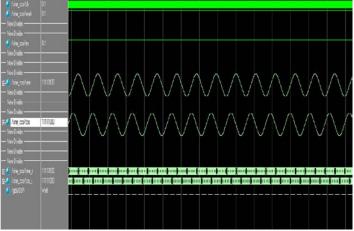

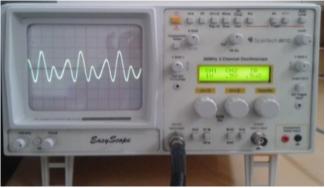

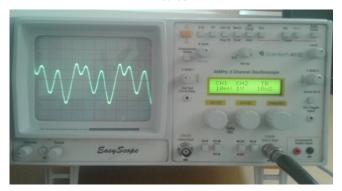

The designed QPSK modulator using Vedic multiplier and carry look-ahead adder is implemented on Spartan3 FPGA kit and the simulated digital output of QPSK is converted to analog waveform by connecting C4 to C21 which converts digital format into analog waveform and this analog output is seen in CRO as shown in the Figure 21and 22.

Figure 21 FPGA implementation of QPSK modem proposed method-1

Figure 22. Output of QPSK modem proposed method-1 on CRO

The QPSK modulation technique using multiplexer concept is implemented on Spartan3 FPGA board Atlys sparten-6 FPGA kit and the analog output waveform is observed in CRO shown in Fig 23 and Fig 24.

Figure 23. FPGA Implementation of QPSK modulation proposed method -2

Figure 24. Output of QPSK modulation proposed method-2 on CRO

**Table 3:** Comparison of three modulation techniques interms of frequency and AWGN on Spartan-3 FPGA board.

| Method                      | Maximum frequency of operation |

|-----------------------------|--------------------------------|

| Conventional QPSK<br>nethod | 146.803 MHZ                    |

| Proposed method-1           | 252.277 MHZ without AWGN       |

|                             | 275.256 MHZ with AWGN          |

| Proposed method -2          | 343.389 MHZ                    |

**Table 4:** Comparison of three modulation techniques in termsofFrequency and AWGN on Spartan-6(Atlys) FPGA board.

| Method                      | Maximum frequency of operation                    |

|-----------------------------|---------------------------------------------------|

| Conventional QPSK<br>method | 291.911 MHZ                                       |

| Proposed method-1           | 438.779 MHZ without AWGN<br>475.556 MHZ with AWGN |

| Proposed method -2          | 446.100 MHZ                                       |

## **V CONCLUSIONS**

With the proposed methods 1 and 2 compared to conventional modulator design (using arithmetic adder and multiplier respectively) there is a great improvement in the throughput. In proposed method QPSK modulator-1 Multiplier and LUT's are used for carrier generation and arithmetic multiplier, arithmetic adder is replaced by Vedic multiplier and carry look-ahead adder respectively. In second method multiplexer concept is used to design QPSK modulator. All these methods are successfully simulated on Xilinx ISE 14.7 software and implemented in FPGA Spartan-3 board as well as Spartan 6 kit. The power consumption, timing and area utilization achieved in the proposed method QPSK modulator-2 also gives a high throughput as shown in Table. The FIR LPF for proposed method-1 QPSK demodulator is designed by using Hamming and rectangular windowing technique in MATLAB with AWGN and demodulation results are obtained and the whole module is implemented on Spartan-3 XC3S400 and Spartan-6(ATLYS) FPGA hardware. The designed QPSK modem using proposed method-1 and proposed method-2 gives better performance over conventional QPSK method as discussed and also these designed QPSK modem gives better results when implemented on Spartan-6(ATLYS) FPGA board compared to Spartan-3 FPGA board.

## REFERENCES

- [1] Prashant D. Thombare , Ameed M. Shah "Low Power QPSK Modulator on FPGA" International Journal of Avanced Research Computer Science and Software Engineering, Volume 4, Issue 1, January 2014.

- [2] Poornima M. Patil, S. K., Shivukumar, S. K., & Sanjay. "Implementation of multiplier using Vedic algorithm"International Journal of and Exploring Engineering, 2(6), 219-22, .2013.

- [3] Sowmiya, Nirmalkumar, Dr.S. Valarmathy, Karthick.S "Design Of Efficient Vedic Multiplier by the analysis of Adders", International Journal of Emerging Technology and Advanced Engineering, ISO 9001:2008 Certified Journal, Volume 3, Issue 1, January 2013.

- [4] Mandadkar Mukesh, Lokhande Abhishek, Prof. R. R. Bhambar, "QPSK modulator and Demodulator using FPGA for SDR "International. Journal of Engineering Research and Applications, Vol. 4, Issue 4, Version 1,2 pp.394-397. April 2014.

- [5] Simon Haykin "Communication Sytems", Fourth Edition, John weily, 2008.

- [6] Samir Palnitkar, "Verilog HDL: A Guide to Digital Design and Synthesis", 2nd Edition, Prentice Hall, 2003.

- [7] Mr. Swaroop A. Gandewar1, Prof. Mamta Sarde," Design of 8 Bit Vedic Multiplier for Real & Complex Numbers Using VHDL" International Journal of Engineering Research and Applications (IJERA),International Conference On Industrial Automation And Computing ICIAC- 12-13, April 2014.

- [8] Patro Arun K., and KUNAL N. Dekate "A Transistor Level Analysis For A 8-Bit Vedic Multiplier." International Journal of Electronics Signals and Systems 1, no. 3, 2012.

- [9] Preksha R. Kolankar, Swati V. Sakhare, "A review on FPGA Implementation of Low Power QPSK Modulator by using Hardware Co-Simulation" International Journal of Engineering Research and Applications, Vol. 4, Issue 2, Version 1, pp.458-461, February 2014.

- [10] Song, Wenmiao, and Qiongqiong Yao "Design and implement of QPSK modem based on FPGA." Computer Science and Information Technology (ICCSIT), 3rd IEEE International Conference on. Vol. 9.IEEE, 2010.

- [11] Michael D.Ciletti "Advanced Digital Design with the Verilog HDL" 2003

- [12] U.Meyer-Baese "Digital Signal Processing with Field Programmable Gate Arrays" Third Edition, 2009.

- [13] B.Krongold, TimomPfau, N.Kaneda and S.C.Jeffrey Lee "Comparison Between PS-QPSK and PDMQPSK With Equal Rate and Bandwidth", IEEE Photonics Technology Letters, Vol.24, No.3, pp.203- 205 Feb, 2012.

- [14] G.Elamary, G.Chester, J.Neasham, "A Simple Digital VHDL QPSK Modulator Designed Using CPLD/FPGA for Biomedical Devices Applications", Proceedings of the World Congress on Engineering 2009, Vol.1, ISBN:978-988, July, 2009, London, U.K.

- [15] M.Kovac, J.Kolouch "BPSK, QPSK Modulator Simulation Model", Thesis, Doctoral Degree Programme, FEEC BUT, 2004.

- [16] M. L. Welborn, "Direct Waveform Synthesis for Software Radios," IEEE Wireless Communications and Networking Conference WCNC. 1999, vol. 1, pp. 211-215, September 1999.

- [17] C. S. Koukourlis, J. E. Plevridis, J. N. Sahalos, "A New Digital Implementation of the RDS in the FM Stereo " IEEE Trans. Broadcast, vol. 42, pp. 323-327, December 1996.

- [18] Umesharaddy, B K Sujatha "Performance Improvement of QPSK MODEM Implemented in FPGA" 2015 International Conference on Smart Sensors and Systems (IC-SSS), IEEE Conference publication. Pages 1-6, DOI: 10.1109 /SMARTSENS.2015.7873621, December 2015.

- [19] A.M.Moubark, Mohd. Alauddin Mohd Ali, Hilmi Sanusi and Sawal Md. Ali. "FPGA Implementation of Low Power Digital QPSK Modulator Using Verilog HDL", Journal of Applied Sciences (JAS-2013) Vol.13, Issue 3, pp. 385-392, 2013.

- [20] V.A. Chandrasetty, VLSI Design: A Practical Guide for FPGA and ASIC Implementations, Springer Briefs in Electrical and Computer Engineering, DOI:10.1007/978-1-4614-1120-8\_2,Science+Business Media, ©Springer, LLC 2011.

- [21] T.Sakla, D.Jain, S.Gautam "Implementation of Digital QPSK Modulator By Using VHDL/Matlab", International Journal of Engineering Science and Technology, Vol 2, Issue 9, pp.4827-4831, 2010.

**Umesharaddy** received the B.E. degree in Electronics and Communication Engineering from T.C.E. Gadag, VTU University, in 2003, Masters in Technology in VLSI Design and Embedded Systems from

K.L.E.C.E.T Belagavi, VTU University in 2006. He is currently working as Assistant Professor with the department of Telecommunication Engineering, M.S. Ramaiah Institute of Technology, Bangalore since from 2007. His area of interest is VLSI Design with Communication.

**B.K.Sujatha** received the B.E. degree in Electronics and Communication Engineering from S.J.C.E. Mysore, Mysore University, in 1987, Masters in Engg.in Electronics Engineering from U.V.C.E., Bangalore University in 1993 and Ph.D. in Electrical and

Electronics Engineering Sciences from Visvesvaraya Technological University (VTU), Belgavi in 2010. She is currently working as Professor with the department of Telecommunication Engineering, M.S. Ramaiah Institute of Technology, Bangalore. She had served as teaching faculty at SJCIT, Chickballapur, for 16 years till 2004. In 2004 she joined MSRIT as Assistant Professor in the department of Telecommunication Engg. Currently she is Professor in the same Department. Her research areas include speech & audio signal processing, statistical signal processing and modeling, Image processing and multi-rate systems, wireless communications, VLSI. Currently, she is guiding 05 research scholars (registered under VTU-Belgaum) in this area. Two research scholars have got their doctoral degree under Jain University.

Parts of this paper were presented at the IEEE 2015 IC-SSS Conference [18]. In this paper [18], performance improvement of QPSK modem was implemented in FPGA without considering the noise element and conventional multipliers and adder were used. In the current paper, performance improvement of QPSK modem is being implemented in FPGA by adding Additive White Gaussian Noise (AWGN) and replacing conventional multipliers and adder by Vedic array multipliers and carry look-ahead adder.